Learn about the key differences between RISC and CISC processor architectures and why they are currently complementary, not antagonistic, concepts

To the CISC architectures AND HEATING refer to the complexity of instructions (commands) that CPUs designed in that standard can execute. The easier it is to program at a high level, the more complex – and expensive – it will be to develop the program hardwareand viceversa.

Each was developed to overcome specific obstacles to the advancement of computing; over 50 years they have exploited each other’s concepts, but also some basic elements of their original designs. OR Canaltech I spoke with Pietro Colloca, Engineer at Intel Artificial intelligence specialist and IoTto highlight their specificities and help identify each of them even in a possible “hybrid” future.

“Both RISC and CISC are called ISA, Instruction Set Architecture. It is basically a standard designed to define how the computer will work,” the Intel specialist pointed out.

Complexity and size of instructions

The first notable difference between CISC and RISC computers is, of course, the complexity and size of the instructions. While RISC machines rely on simple instructions with predetermined sizes, CISC processors use much more complex instructions, transforming basic commands into instructions embedded in more complex commands.

A basic sum operation in RISC, for example, would involve independent commands to load data into different registers, add the values, and load the result into the destination register. In CISC, the “SUM 2 and 5” command combines all intermediate instructions into a single line of code.

Hardware complexity × code simplicity

CISC computers were developed to facilitate application programming, and this is why new, increasingly specialized components were added with each generation. By making the hardware highly complex and with a series of coprocessors embedded in the silicon, it is also possible to incorporate smaller instructions as pre-programmed steps of larger, more complex instructions.

For this reason, performing a simple addition operation in RISC requires multiple lines of code, while in CISC it requires only one. This same reasoning applies to all other computational operations, such as inferences, conditions, information flow, and logical operations.

“Explaining a little further CISC, even though it has this ‘complex’ in its name, it’s here to make things easier. Within the architecture itself, it has different instruction sets, which are basically the mathematical operations that the computer can perform the execution. Instead of writing in a RISC architecture “I would like to load this information into register A, load this information into register B and perform multiplication”, we simply enter “multiplication” and the processor performs the complete operation “, explains Colloca al Canaltech.

Therefore, all the more complex hardware, the more complex the operations, the simpler the programming for that system will be. On the other hand, excessive complexity makes the production process relatively more expensive, difficult, and its operation usually consumes much more energy.

It implies the adoption of the RISC architecture, since it requires a syntax closer to machine language Software extremely complex, longer and more detailed.

Memory × Registers

Because it has no specialized accelerators, all instructions in RISC are executed directly by the processor. To be able to execute all the commands of the architecture, the RISC CPU design requires a much larger number of physical registers, since interdependent operations must be loaded in parallel to execute immediately after a previous command is executed.

In CISC the same does not happen, since all operations of a more complex instruction are loaded and executed directly in the system’s memory, with only the results stored in registers. For this reason, RISC processors require less memory, but many more registers, while in CISC the proportion is reversed.

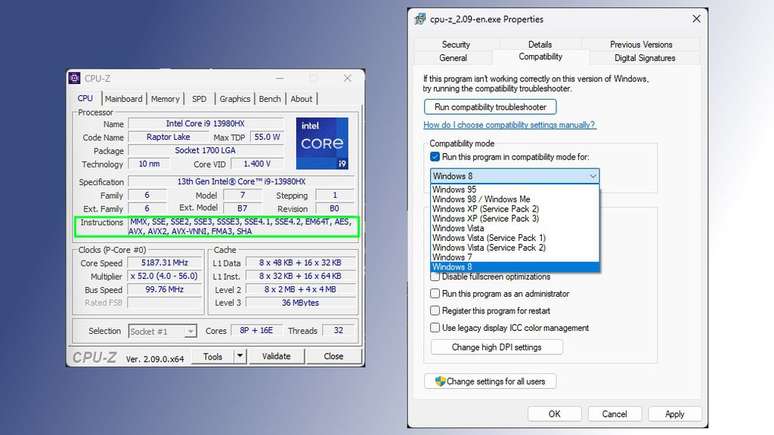

An Intel Core i9-10900k processor, for example, has 16 single instructions and multiple data (SIMD) registers, with each hyperthreaded core also having 16 SIMD registers. ARM processors, in general, can have between 32 and 192 registers per core depending on the design.

Memory access

Since all instructions in RISC are executed immediately at the register level, plus the system is less dependent on memory, the processor does not need direct access to memory. The difference is one of the advantages of ARM processors in terms of efficiency, as memory speeds are usually much slower than those of ARM processors processor.

By not depending on loading and executing instructions on slower components, RISC processors tend to consume much less power. This is ideal for low-power embedded systems, such as IoT devices, smartphones or even servers where every Watt makes a difference in the total cost of ownership (TCO).

Computational cycles

When Let’s talk about frequency of CPU, in fact, we are describing how many computational cycles are performed in one second. A processor with a base clock of 2.9 GHz, for example, performs 2.9 billion cycles per second, with values that can exceed 5 billion cycles in intense tasks.

For this reason, execution in single RISC cycles is among the main metrics to justify which types of uses the architecture is most advantageous for. In short, because it runs with fewer instruction sets and with much simpler instructions, each of them is always executed in a single cycle – that is, a RISC CPU operating at 2.8 GHz executes 2.8 billion instructions per second.

In CISC this changes a lot, especially because instructions have variable sizes. Some of them can be executed in a single cycle, but most require multiple cycles to execute.

For this reason, Intel has implemented the hybrid core standard in the new x86 processors. big small, with some aimed at simple performances, and others at complex performances. Indeed, the commands closest to the machine level and which can be executed in single cycles, even in CISC, are directed to the efficiency cores (E-core), while the rest of the commands are processed by the performance cores (P-core ).

Backward compatibility

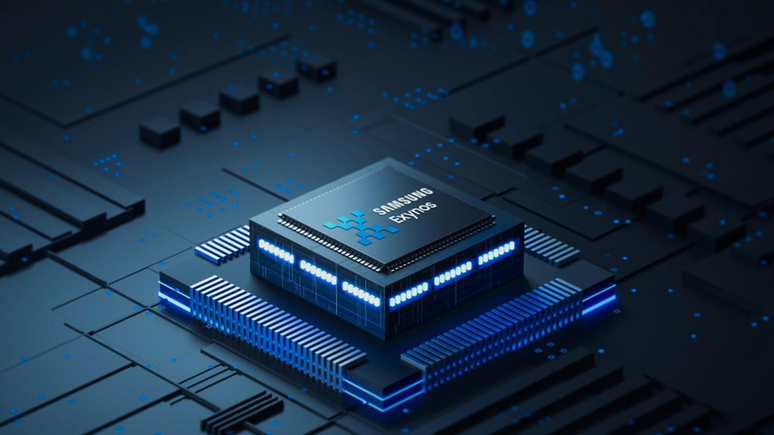

Another inherent advantage of the CISC architecture is that there is no need to change the original microcodes with each new generation of processors, since most of them are built into accelerators. This way every modern x86 processor already has the ability to run the same codes as older machines.

“[A Intel] we introduced the x86 architecture in 1978, with the 8086, and as we progressed, we added things, like our accelerators: MMX, SSE, AVX2, and so on. This is precisely to simplify the mathematical operations [no nível do hardware]. We use accelerators to make it easier to write and run codes,” explains the Intel specialist.

In RISC, to ensure the smallest possible number of instructions, each generation must be reprogrammed to some extent, removing old microcodes to insert new ones. This means that most RISC processors are not cross-compatible and are designed specifically for their functions.

One NVIDIA ARM CPU of extraordinary gracespecialized in inference operations for artificial intelligence, it does not have the same instructions as a processor Apple ARM M2, For example. Although they are two extremely advanced and top-of-the-line RISC products for their segments, they cannot natively perform the same tasks as each other.

Complementary architectures

In practice, CISC and RISC were developed at different times to address different computational limitations. However, both evolved side by side, absorbing each other’s improvements whenever possible.

“[Nas CPUs Intel] There are two different x86 architectures, Golden Cove and Gracemont are focused on different purposes, while P-Core will have capabilities such as hyperthreading, E-Core aims for greater efficiency. [Comparando os big.LITTLE ARM e x86] the concept may be similar, but when assembling it it is not the same”, underlines Pietro Colloca.

The example of architecture big small, is even the main one in these cases, since it was initially adopted by ARM processors for smartphones, and was adopted by Intel starting with Alder Lake chips. In parallel, the ARM M1, M2 and M3 processors Applethey still use the RISC architecture, but have almost the same number of transistors as x86 CPUs in CISC, and also work with more complex instruction sets to make programming on the platform easier.

The trend is for the two architectures to be increasingly combined, and the key point to differentiate them is more a question of advertising than, in fact, of technical specifications.

Source: Cloud Computing: Theory and Practice 3rd edition, Dan Cristian Marinescu; Educational.io; Engineersgarage.com; Spices; Stanford University; University of Tennessee; AHIRLABS; IBM;

Trends on Canaltech:

- Popó x Kleber Bambam | How to watch the fight live?

- The Y chromosome is disappearing from the human species

- The presence of lead in the Stanley Cup leads to the company being sued

- Xiaomi launches the CW500 security camera with low price and rain protection

- 10 Cool Commands to Use in Gemini

- Scientific article with strange AI images is removed

Source: Terra

Rose James is a Gossipify movie and series reviewer known for her in-depth analysis and unique perspective on the latest releases. With a background in film studies, she provides engaging and informative reviews, and keeps readers up to date with industry trends and emerging talents.